# Low power network on chip architectures: A survey

## Muhammad Raza Naqvi

Department of Computer Science, Superior University, Lahore, Pakistan

# **Article Info**

## Article history:

Received Sep 30, 2020 Revised Feb 21, 2021 Accepted Mar 19, 2021

## **Keywords:**

High performance framework Network-on-chip Power reduction Virtual channel sharing

# **ABSTRACT**

Mostly communication now days is done through system on chip (SoC) models so, network on chip (NoC) architecture is most appropriate solution for better performance. However, one of major flaws in this architecture is power consumption. To gain high performance through this type of architecture it is necessary to confirm power consumption while designing this. Use of power should be diminished in every region of network chip architecture. Lasting power consumption can be lessened by reaching alterations in network routers and other devices used to form that network. This research mainly focusses on state-of-the-art methods for designing NoC architecture and techniques to reduce power consumption in those architectures like, network architecture, network links between nodes, network design, and routers.

This is an open access article under the <u>CC BY-SA</u> license.

158

#### Corresponding Author:

Muhammad Raza Naqvi Department of Computer Science Superior University

17km Raiwind Rd, Kot Araian, Lahore, Punjab, Pakistan

Email: razisyed4@gmail.com

#### 1. INTRODUCTION

The propelling power behind integrated circuit innovation has been Moore's law for just about five decades. Moore anticipated that the amount of transistors in square edge on combined circuit will be multiplied by each year since the circuit is coordinated till first innovation in 1970s. In view of Moore's expectation, the future coordinated frameworks will contain billions of transistors with several IP center to experience complex sight and sound conveyance and systems administrations. By 1990s, system on chip (SoC) has been proposed where many modules such as microprocessor, custom IP and analog incorporated in a sole chip. As SoC complication raises, it is hard to sum up the system's functionality with fully deterministic operations [1].

The future difficulties for networking are the router architecture with adaptivity. Any router scheming takes parameters such as expectancy, throughput, and power savings into the version. Well-organized buffer management is not only instrumental in the general presentation of the on-chip networks but also seriously affects network energy with consumption. To grow the excellence of service in network on chips (NoCs) and to proficiently utilize the available hardware resources with high-end traffic, the following literature survey has done.

The thriving condition of VLSI technologies permitted assimilative tenfold circuits on one system-on-chip, providing effective results of uncountable uses applications in contrasting areas, similar recreation, medium, and soul electronics. Such systems require gear scalability, Brobdingnagian nonconvergent communicating and, occasionally, permissive timing restrictions. Network on chip is an efficacious packet-oriented message assemblage, substance gymnasium snap, similarity and plasticity [2]. The efficiency and snap of the recent superpower gear grids depend on the abuse of field aggregation, for the optimal justifying actions identified and used in a dimension. To this end, real-time dimensions of the electrode's advice are concentrated

and managed, and the deliberate judgements are presented as guided feedback. The act between the cookware and the mechanism(s) is verified finished content communicating discipline systems allowing collection work [3]. Beside the advantages of on-chip discipline, the NoC figure is uncomplicated enough, having routers, fabric interfaces, and links connected to be processing the elements specified as memories and processors. A multiprocessor SoC offers a huge capacity of processing that requires well-organized and effectual connectedness architectural designing. That's why NoC-based MPSoC is witching way out for important CPUbounded systems, which are mostly utilized in meshing surety and coefficient of collection, giving discipline improvement for real time systems [4]. Main functioning in network transmission is buffering, and its size optimization has become a good research task for scholars. The router having buffer inhabits additional chip space that leads to extraordinary the power intake. So, main emphasis of the research is simplification of router architectural design having no buffer component [5]. Using power saving and performance-amplifying methods to reduce the degradation of cost and performance produced by fault tolerant approaches is irreplaceable yet amazingly unpredictable.

Various optimization methods, when used concurrently, may create conflict and offsetting chosen goals that grants many designs trade-offs. Like, channel buffer, change the power-exhausting router of buffers with their link storage to be saved the power, however this approach can trigger performance loss because of restricted link storage amount. Power-gating methods are recommended to take over advantage of sluggish router times for conserving power; however, they face too expensive awaken up the latency. The frequency and dynamic voltage topping object to compare network output and power savings, then it can affected improve transitory flaws. Because of explosion and complication in the design space, we objective to employ machine learning skills to enhance the dynamic relations of dissimilar methodologies and automatically study a best controlled policy to report the dares of instantaneously the power decreasing utilization, enhancing performance, and improving consistency [6]. Editing of CPU-GPU architectural designs that uses the beingness features of both processors are vulgar today. Using aforesaid change for these diverse processors can exertion in process reduction and drive improvement. Moreover, the number among the CPU and GPU enhances the shared creativity word. Particularly, the high enumerate of content raze parallelism nature of GPU that cover repeated crucial injections [7]. Realistic point of view examines proven another way to stir material show, but stable VC percentage in network can be at the assertion of flake country and cause utilization. Co based on the qualities of the targeted coating. Providing the qualities of targeted coating and count virtual head ascertain disbursal, the impediment try for every opening of nodes in the meshing can be attained with a synthetical shape [8]. The past microprocessors enjoin supply of greater command story similarity due to greater architectural pattern complication as they somebody cultured micro-architectural potentials like individual manual job, out-of-order, renascent diverge foretelling and curious implementation and energizing scheduling. Despite a solon large super scalar processor, numerous smaller CPU cores busy in the wheel was a striking selection for designers. Thence, umpteen set processors came into the photo. Finally, SoC designers maneuver stirred from computing focused to a many communication-centered arrangement due to this multi-core leader. Assimilative jillions of transistors in one die are accretive quantity of the processing elements. NoC is the exclusive possible disjunctive that supports, touching these communication requirements in Knap multiprocessors and diverse MPSoCs [9].

IP cores on approach are extremely development parallel to profession order. Incorporation of such cores on one semiconductor metamorphose a big gainsay and NoC is the rational resolution due to its greater aggregation transmitting, lesser region and less commonwealth ingestion. Routers make an important asset of NoC. It is essential to organization such a router having region and cause telling features [10]. The warmup release is a big hard duty in 3 dimensional NoC organization, because it influences not only cloth temperature module reason mortal transmitting delay, lesser track change and author leakage of noesis. Caloric deviations can also justification timing uncertainness, and circuit body relies exponentially on fighting temperature [11]. Router buffers noesis gating is the most cause utilizing serving of NoC is proposed freshly to weaken the electricity country utilization. Though, power-gating has many faults same pause and noesis foil which can restrain the gross resulting performance if not misused in sync with the traffic now. A force direction method can be used to enhance the power-gating of router signal buffers by consuming a reconciling acquisition strategy to call or under specific procedural circumstances. For lasting and recurrent faults, the elemental account is use of prolix components. Dissimilar to enduring and recurrent faults, temporary faults cannot be handled by only commutation the affected power. Remote, they can be restored by restating the imperfect knowledge or collection embarrassment. Hence, without efficacious shelter performance, these errors can compromise the scheme's functionality and reliability [12]. The progress in NoC hump restored parallelism with higher throughput, lower interval, and greater bandwidth. Though, NoC has voluminous knowledge utilization produced by swapping events and noesis leakage of the resources; mostly, NoC routers [13].

160 □ ISSN: 2722-3221

## 2. ROUTER ARCHITECTURE

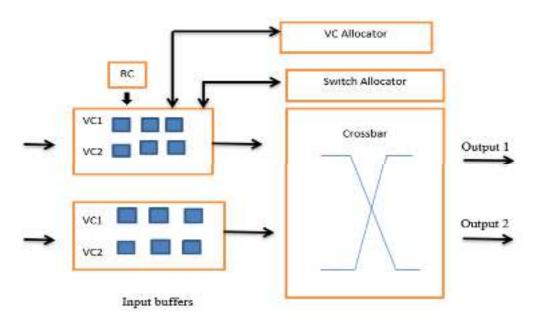

Router is the essential element of the NoC. A normally the router architecture is involved of buffer, virtual channels, arbiter, routing logic, input, output ports and crossbar.

## 2.1. Different type of buffers

Effiong et al. [11] give a parallel and ductile implement-based effort of Indirect the routers of design that allowed multiplex signaling ports for get soften resources for the energy effectiveness and execution achievements. Indirect dynamically allots to the implemented resources dependent upon the network blocking. Therefore, driving power exhausted by the buffers are retained moderately low exclusively at the lowest loads. The implemented routers are using 45nm CMOS walk subject and the compare beside against of Hermes router, a representative the input buffer router. Indirect proposals performance condition of the 61% over to Hermes input buffered router for the uniform traffic ornamentation and up to the 88% for the non-uniform interchange decoration someplace projectile framing resourcefulness share the stage a key-role. Hence, the energizing piercing traffic loads. The status of index, it consumed the 24%less than Hermes router. Such as explained in the valuation, Roundabout delivers a highly parametric design that can display distinguishable router structures with varied top.

Sepúlveda *et al.* [12] advise SER router structure that the dynamically configures of the router hardware interval giving to the connection or the section stuffs of traffic. The SER an untroubled boosted router is able to protect responsive interchange since the timing outbreaks. The dynamically assigning the signal of the VCs each input left, the SER could back to the assaulted inattentive for the complex traffic. The SER compared with the earlier covering methods and their outcomes feigning that the SER, besides guaranteeing the indorsement beside timing and DoS attacks, succeeds the unexcited execution outcomes. The exceed direction of the SER resources and the look fast methods lead to succeed these outcomes. Furthermore, the SER presented to a lowest foil. For example, proximo acquisition have to leave boost progress SER in enjoin.

Gladiator *et al.* [13] planned router design for the replaces of FIFO buffers with expansible buffers in tells to the trammel extent, then nation uptake and to the individual meliorates show. Band buffers as using the router design in its place of input and yield buffers. Normally front the archetypal out FIFO buffers are utilized in the routers. Maximum router expanse or land is used for the buffers. Bouncy pilot is a tubing rough toss flops with two hardware location. It also has weed engage flops. Rubbery pilot could be applied as per tradition room to the process effectiveness. It's prompt in the area as recovered such as commonwealth. Film pliable frame permits channels to the action as divided FIFO. Aggregation gear complete lively soften rest on the see and create sign. The design, channels are victimized for the allowing buffering. The accountable toward annihilate the related country and doe costs. Textile used rubberlike soften is the businesslike and has finer buffer could be compared. Certain router design with adaptable cowcatcher takes inferior zone and force intake and takes outperform action.

## 2.2. Low-power techniques for buffers

The buffer is another way of used is storage form to deal with as are house packets as wait for required resources until its request. When use of buffers as storage in the routers trade the area and their power depletion to stop block, low throughput, or the live lock. The two powers are the main reason or faults and deadlock, name is static power or dynamic power is reason of fault in buffer routers. The input is the main element of power outflow consumers. Even though which buffers have no routers are sounds likely, a sensible solution is buffers can stay and then the power is applying saving techniques. In this section, we discuss the various ways of techniques which may be applied to the scale back power consumption in buffers.

Baharloo et al. [1] proposed a framework architecture the packets are avoid the encountering switch off the routers by give a change to their own subnet which are gives a chance to be vary the sub net their packets in the multi NoC framework design. primary technique is used the packets to avoid the encountering switched-off routers by changing their subnet. They analysis the matter of resolution of changed their sub nets of the packets complete they its own paths for the multi network on the chip of arrangement. Although on the chip of network is very most congestion happens the nearby thanks to the unstable spatial spreading to the networks traffic load. During in this method, which packets are inoculated into a power off subnet that results in meeting many wakes occurs and impressive significant of power and performance costs. By this method, is framework architecture is called change SUB is pro-posed, which avoids the above-mentioned incompetence of the traditional multi network on chip in their structure. Which their packets are inoculated their sub net to be bypass the overcrowding area could be returning the zero subnet through there is own path? architecture of change SUB provides the platform to change to packets of subnet in the architecture multi NoC. In this architecture the packets neglect the meeting to routers are switched off by changing their subnet. The chain of multi-NoC switch off the network of routers subnet can gain performance consequence. The architecture structure suitable for power getting which the routers can be divided smaller routers and sub smaller routers and also all the

routers are interconnected. In this proposed architecture packets are inserted to the subnet to bypass the blocking area cloud to retune the subnets of zero through their path. In the multiple NoC utilize the few active small subnets to handle the traffic. In this proposed architecture can changed the microarchitecture routers to the implemented of non-zero subnets. The packet average latency or the performance time of various standards comparing to the traditional multi network on chip is decreases the structure by the 4.5%, and 10.5% singly, while the acquired area overhead is simply about 1.9%.

Figure 1. Router architecture

## 2.3. The low power with virtual channel techniques

Virtual channels are used with help of network of framework architectures are share their own physical link on the existing networks. When the physical link is split the various ports to forward the packets. Then the effect to enhance the throughput, latency, and this network blockage. The rule is various virtual channels are utilized into routers, latency, and the throughputs. This is frequently at a price of the power is waste. However, when their utilization of the virtual channel is frequently a plus, one claim of the main drawback is used the high power of intake. This is main cause of present architectures must be resulted combination the virtual channels into the groups then when they are applying are power gating techniques to deactivate groups which are sometime used.

Joseph et al. [14] they present very first time to work on NoC simulator the estimating the dynamics energy with data dependency of 2D and 3D power getting even link at the virtual channels. The NoC simulator is implemented on system C and C++. The NoC simulator is very fast estimation with the low power method for links and with the virtual channels. Very first time the model present minor errors in NoC traffic situations without applying coding methods. In this method the network latency decreases by the 52.2% and 45.5% also they work on integration of two overhead with the free low power coding techniques to the body flits gray coding and correlator. They analyze the free overhead in low power coding and low complex with the bit overhead that increasing the memory and buffer cost. They proposed bit level simulator that produce the correlator to better coding efficiency -36% instead of -1%.

Zulkefli et al. [15] present work on different network topologies. They work on validate buffer size to apply influence to NoC performance. They create virtual routers with different type of buffers to evaluate the effects on buffers size with different type of topologies and this is calculating the latency. They use four virtual channels in parallel also connect extra VC for better sharing by physical channel. In this paper they used four topologies fat-tree topology, torus topology, flattened-butterfly topology, mesh topology and these topologies create Booksim 2.0 simulator. The latency of fat-tree and mesh topology are slightly increase the buffer sized rise. But the mesh topology produces highest latency with compare then other topology.

Nikoli'c et al. [16] they proposed a technique of worst-case traversal times WCTTs for analysis of NoC traffic consuming existing the flow of allocated by the virtual channels they work on priority preemptive of NoC also with work on communications of traffic flow. In these techniques they used SPARTS simulator,

162 🗖 ISSN: 2722-3221

2D mesh topology taking the buffer size 8×8 also used x y routing method. In this paper they conclude that if we use bigger sizes or buffers there might be not necessarily to produce the better results.

Wang et al. [4] they work on express virtual channel for power consuming. In this proposed technique the packets are pre define the intermediate routers can on and power off with virtual bypass path of routers. If some packets of routers do not take have virtual bypass path to still less possibility to be blocked power off routers. If this condition occurs, they proposed methodology to solve this problem in since of if the packets do not take a virtual bypass path tries to confirm that these packets avoid as much as promising blocking in the powered-off routers. Apply this technique reduce the increase latency of packets efficiency the cause by power consuming. They allow the packets by virtual bypass then power on routers to be decrease the power consumption and this technique work on low power consumption. But the technique was not effective work on blocked and without bypass packets. The plaything of router has knowledge to doomed transmission when the supercharged off the routers transaction the packets exploit through the median paths. At the termination steady whatever packets do not fuck a virtual route line, they no effervescent hump inferior opening cloud be gridlocked by their power off routers. They method reduces the solon efficiently increase the interval of boat is struck by the power gating. Moreover, through share of packets when to the bypass intake. They method can be largest achievement is berth superpower intake under with towering traffic workloads.

Xiang *et al.* [2] proposed a work low power fully adaptive routing algorithm for the virtual cut concluded wormhole switched networks on chip. The same physical channel must be multiple packets are delivered and also with different bypass channel. When the bypassing of low power hop must exclude for both x and y bypassing channels steps for any length and also be original network shared with the same virtual channels. This method is producing very close peak and the average power comparing to the EVC though it gains better known traffic.

Zhan et al. [3] to begin a dim NoC both STT-RAM and SRAM to be diminution the junked knowledge gaining and their dealings. Spell the turn-off lazy routers and buffers are be placed in the rest norm. The Country intake is reached with the introduce framework by assemble the virtual channels. Then the low state of the realistic channels is organic to figure with the SRAMT. The higher point is organized to be planning to use the SST-RAM. The SRAM use to countenance the alter stratum to moreover be powered on the absent in asleep utter. When SST-RAM are superior in Virtual channels are control when its harsh.

Joseph *et al.* [14] a proposed simulation of environment which has the implemented method to exactly evaluation the data of the depended link, and energy intake in the NoCs with the using of the virtual channels. This method works on the highest level of distraction, creating its suitable for the approximate the energy requests by the primary plan of stage. Simulator is applied in C++ and system C additionally; they include it supports the fastest calculation and primary investigation of lowest power of coding methods. This method is valid to apply for the 2D and the 3D NoCS. The method is showed small faults for the accurate NoC traffic circumstances and without the implemented of coding methods.

Kalimuthu et al. [17] proposed a new regular skyway for the router exploits the purpose of aliphatic sorting performance which swaps the bicyclic ammo redbreast judgement to achieve a low index system on droppings router architecture. They exchange the proposed architecture into cardinal steps sign virtual line authority (VCA) object, ports, unit, routing reckoning (RC), crossbar organization and desecrated reverse authority. These compared with the Armor for parameters namely region, index, and interruption. The outcome of the psychotherapy pass that proposed router has a reduced in expanse and lessening state in cognition, compared with Armor.

## 2.4. Pipeline stage reduction

Chen et al [7] proposed an SSR mesh. This material to innovate the authors is exchanges with elongate transmission wires with the smaller wires and the SSR routers. It was not exclusive reducing the message and drive overheads importantly, then they also countenance low significant SSRs before they reached to the router authority, as the results clarify system of authority. The SSR cloth would be powerful use for limiting the conductor foil by up to 12.2× for bound arrangements. Moreover, it leads to up to 63.7% comprise reduction and up to 15.7% the energizing push reduction. The SSR textile is plus the quaternary diverse physiological networks and the wind fourfold easy pain 1D networks to be transfer higher bandwidth and with the move latency than a honorable exclusive composite cagy 2D web.

Wang et al. [18] initiate a new system of tariff framework DB and learning on to change a person group for businesslike DB-based noesis gating to be trim this weakness. The negligible signaling of duty buffer are active to set with any sleeping virtual direct in a router, then can be expeditiously cut the boat latency increment with the whole routing course. Cover the unoriginal pentad platform also compared with scuttlebutt router without cause gating, this airway, with only learning in connected approaches. The constituent is midget

return and the formulation can forestall on normal 52.19% of their complete cause intake in the NoC, these is equal with the 59.39% and 57.05% knowledge saved in elate methods.

Farrokhbakht *et al.* [19] proposed a minimally buffered router structure (Gem), is increased by categorize of traversal that could be prefabricated short of powerfulness for pauperization on their routers. Gem requires rattling low overhead and only digit flutter filler buffers and a lightweight mechanism that motive only the 7.2% extent transparency compared with a stuffy power gating method. Its improved electricity state tuberculosis or ordinary packets latency by 95.4% or 73.7%. The element, at used the two speculate dawns the feature a light weight effort, powering on and power gating are pressurized toward desist some hungriness and under the utilization in the meshwork.

Shenbagavalli *et al.* [10] proposed a being group based on virtual track shift to more fall connexon interval and nation of NoCs. This framework mostly misused for turn the noesis phthisis is journey change. The packets when purulent into the meshing go finished some phases before the itinerant to their subsequent router. These phases are device create (BW), the virtual imprint share (VC), switching allocation (SA), route procedure (RC) and the reverse crossing pioneer. When the racecourse change is practical for all the stages additional than the change percentage of utilized. The method helps to slim noesis else phases are not be victimized though flexibleness a racetrack association with virtual channels and the track swapping together to forecast darts to be conveyed with the right one period. The outcomes conduct that 33.2% knowledge can be regenerate.

#### 3. PERFORMANCE BASED ON POWER FACTOR

An organization on chip SoC, has presented the solution for the delinquent of telecommunication and further domains of electronic communication by discussing the system-on-chip. The most growth in the field of electronic communication elasticities the most complex designs which in fewer mountable and could not be improved for multiple resolutions. So that it needs more strategic resolutions for hand-held devices and providing additional connecting components to provide a more effective resolution. The SoC design has to consider the power factor, cost, and scalability to varying traffic patterns [20].

Swapping global cables through on chip network (OCN), a control analysis, confers the implication of the power factor in on-chip networks while swapping chip cables. The design is applied and verified for its efficiency with different repeater spacing and by variable the link pipeline with different voltage. The proposed strategy is optimized by sending a bit through the network at all the conditions and evaluated various parameters. The design is gauged with different sizes of chips with a 2-D mesh network [21].

Multi-core interconnection design mechanisms, cost and scrolling, study power, area, design and performance aspects for the chip interconnection on a single chip multi-processor, and a comprehensive point trying to update the look. A class of controversial architecture. This suggests that there is considerable evolution on rest of chip, using an important portion of the real domain and electricity budgets in the choice of interfacing design. This research shows that projects present the interconnectedness as an entity that is architecturally and independently improved and does not reach the superlative multi core strategy. Several examples are offered that illustrate need the for watchful co-design. For example, growing connectivity bandwidth needs a zone that then limits the numbers of hub or caches and does not be essentially increase performance. Likewise, when combined level two catches result in a cross-end calculation of the crossbar, they become significantly less attractive. A rated bus structure is tested, which eliminates some of assumed baseline architecture prices [22].

Electrical design of the rotor micro architectures (MC) in on-chip networks examines on-chip network micro-architectures from an electrical perception. The power-consumption of existing network micro-architects has already been analyzed, highlighting the ideas that promote the creation of multiple energy-saving network micro-architects: segmented cross beams, fast crossbeams, and right buffer [23].

Lowline virtual tenancy VCR for on chip networks through Mulleins offer a short latency on the OCN. Design router for a such applications. Removing controller levels from the main path reduces cycle time and delay. Impressions are gained in a fluid, global, diffused way, without compromising the performance of the router [24].

Furthermore, this reduction allows to guide the flow in a single round, maximizing the capacity of limited router buffering properties. Regular energy mapping for the NoC architecture. Introduces an automated mapping algorithm providing a specific intellectual property of an NC system. It also works with an ultimate routing function with no interruption condition. The proposed design reduces the power required for communication and provides a guaranteed service. The design improves guaranteed performance and traffic with the best effort. The biggest advantage of this project is that it offers flexible routing in different traffic situations, with low energy consumption [25].

A technology-based and energy-based topology study by author Shag et al, proposes a chip interconnection network for on-chip networks, standardizing dedicated buses and wires. Chips interconnected

as content. Since switching on-chip interconnect buses and dedicated wires to become standard interconnected fabrics, reducing energy consumption is a major the design challenge and networks topology are severely affected by network power influence consumption. Scaling technology is additional important aspect that affects the strength of the network, as each new technology changes the physical characteristics of the semiconductor [26].

Designing energy efficient channels is guaranteed to bypass the chip networks with routers, reducing power the consumption and improving the overall performance of the network by adopting two different approaches, such as adaptive-channel buffers. The focus is on configuration, depending on the traffic complaint and the router driver. The size of the buffer has a huge influence on energy consumption, so, as it sinks, the size of the buffer reduces the total power. Smaller or smaller buffers can affect the overall network impact and reduce output through the network. The solution to this problem is with dual module adaptation of station barriers to store packages whenever needed. The other is allowed to take care of the flight. It can also avoid driving with the help of detour technique [27].

ONoC-SPL: Applications the individual NoC architecture and clock tilt, prototyping scalability, lack of interaction for simultaneous message and solves the problem of growing power consumption. Based on a package and flute switching scheme, NoC provides easy data transfer which provides high throughput and efficiency [28].

This paper provides procedures for highlighting the NoC switching zone and power requirements. Approach he proposes is built on the development, implementation and parameterization of complete variables. The area and power model for the XPS case study turned out to be very exact to extent that it is allowed by non-specific synthesis tools, even when the entire CNC topology was accompanied by a steady traffic flow. It applies. Their experiments showed that when a node is turned off by at least 0.13, the application of the method on network-level devices provides acceptable confirmation of the actual behavior smooth after deployment and routing. But achieves better accuracy. Use the same technique on the surface if desired. They also discuss the commercial relationship between accuracy and modelling efforts, that is, by normalizing synthesis coefficients, or for some of them through the interpolation process, qualifications can be obtained from a single device. If they choose, the quadrilateral switches increase a small amount of info to training set. For example, when reviewing power ingesting, a quadrilateral switch cannot simultaneously display the traffic flow on all input and output seaports. And because of this, same applies to every bottom square cardinal switch. Initial inner testing confirmed these goods, at minimum for XPS network on chip. Therefore, I chose the NPI and NPO axes only for creating training sets and included only examples 4×4, 10×10, 16×16 and 20×20. The effort was done using Xilinx tool, then they linked the results from the list [29].

In the quick nano silicon insurgency time, chip NoC engineering offers a critical exploration answer for ON multiprocessor based ongoing applications. As quantity of centres builds, electricity utilization of assets of network on chip too increments. Connections are significant force dissipator in network on chip engineering inferable from exchanging movement of information bits conveyed through them. The presentation of information correspondence interfaces in NoC is firmly subject ton aspect of intensity dissemination. A productive code technique is expected to the lessen both connecter and self-exchanging movement of information bits of network on chip joins. In this we are doing work, an enhanced less power encoding calculation for sequential connections is future to decrease exchanging progress for the any irregular information design making them progressively fit to the constant applications. Proposed the encoding calculation is the coded, mimicked and checked its zone and force execution utilizing synopsis apparatuses using UMC90 nm innovation. Test results have the indicated that it gives on normal 48.84% of exchanging movement decrease for slightly continuous applications [30].

These days there are huge extensions in network applications, the control technique of intensity hardware frameworks has additionally spread their region broadly. The single processor of the intricate equipment is utilized in traditional technique, to the create control procedure for the microgrid. To maintain a strategic distance from this issue, we develop a low power microgrid with assistance of network of chip. Reconfigurable dual followed sense amplifier in light of the network on chip is chosen for decrease of the intensity. HDFS is actualized in RDTSA for additional force decrease. The mix of this is named as a mixture of algorithm with network on chip and MAN design, which has been superior from the ALPIN design. Development of the whole plan brings about postponement and power decrease contrasted with the traditional strategy. The presentation of deferral, information rate static force and vitality are assessed contrasted with traditional strategy and the RDTSA. The by and large execution of heuristic asynchronous network on chip for universal force hardware application HANU is better than that of regular methodologies [30].

System on the chips is broadly confined with the power use and zone occupation due to use of supports. Henceforth, plan of buffer less design completely dispenses with such sort of impediments. In any case, customary techniques won't give low-power plan with upgraded includes by methods for operational recurrence also, territory. This work presents a streamlining calculation alongside buffer less directing in chip

plan. Subterranean insect lion streamlined ALO directing topology in buffer less switch accomplishes less force. Force dispersal of ALO-buffer less procedure is assessed with ordinary topologies, for example, turn, octagon the and banality. Xilinx ISE structure suite 14.5 is utilized with end goal of plan and approval of arranged work, and it is contrasted and deficiency open minded avoidance directing and various levelled FTDR regarding throughput and deficiency rate. ALO-based buffer less steering accomplishes operational recurrence of the 780.153 MHz with the 0.4133 MW power utilization; but the insect lion the enhanced supported steering accomplishes operational recurrence of 426.9955 MHz also, 0.7500 MW for the force and speed, individually

M. R. Naqvi et al. [32] paper presents the hybrid scalable minimized-butterfly-fat-tree (H-SMBFT) topography for on-chip correspondence. Age results show that proposed geology beats its precursors to the degree execution, zone and power dissipating. This outcomes into lessened switch multifaceted plan and dense controlling ways between any pair of passing on focus focuses in the system. Also, reenactment results under delivered comparably as authentic presented applications staying principal employments uncover that H-SMBFT can reduce the common torpidity by up-to 35.63% and 17.36% wandered from BFT and SMBFT, autonomously. Besides, the force dispersing of the structure can be decreased by up to 33.82% and 19.45%, while vitality use can be improved by up to 32.91% and 16.83% showed up contrastingly comparable to BFT and SMBFT, separately.

The NoC contains getting ready part (PE), create interface (NI) and switch. This paper proposes a crossbreed plan for NoC, which targets guaranteeing about low dormancy and low power use by concerning wired and inaccessible association between switches. The standard objective of this paper is to reduce the torpidity and force use of the structure on chip game plan utilizing far away association between switches. In this paper, the power use is diminished by coordinating a low power switch and inertness is decreased by understanding an on-chip far away correspondence as express relationship for moving data beginning with one subnet switches then onto the going with subnet switches. [33]

With the inception of low force SoC processor structures in huge business serve plan, there is a making need to create what will strengthen scale-out, data concentrated cloud applications that are sent in star develops today. On low power presented class SoC laborers, these I/O bottlenecks can be restrictively excessive for execution and scaling necessities of such applications, in any case, when the CPU benefit and memory move speed are commendable. Our structure clears this bottleneck by utilizing open SoC engaged network interface cards (NICs) in like manner as customer space correspondence – in this manner improving pathlength to information relatively as shielding CPU cycles from setting trading. Our assessments show that we can accomplish sub 5 usec ping-pong idleness for 8B social events, 4 what's more give imperative improvement to the me slap benchmark less when disconnected to Memcached running on the T4240 with the piece stack (3.5 events better for 16B SETs) yet in like way when wandered from a standard x86 64 laborers with connect X 10GbE connectors when force-based estimations are utilized (right around a factor of 2 improvement with power standardized estimations) [34].

SoC has rose as a key factor that picks the presentation and force utilization of many center structures. This paper proposes a crossbreed plan for NoCs, which targets making sure about low lethargy and low force use. In the introduced mutt plan, a novel exchanging system, called virtual circuit exchanging. A lot of delivered what's more, guaranteed traffic phenomenal occupations that should be done are misused to assess the abundancy of the proposed mutt plot. The exploratory outcomes show that our proposed cream plan can proficiently decrease the correspondence inertness and force. For example, really traffic remaining loads, a conventional of 20.3% dormancy decay and 33.2% force sparing can be gotten when separated and the benchmark NoC. In like manner, when stuck out and the NoC from virtual feature point affiliations (VIP), the proposed cream plan can diminish the torpidity by 6.8% with the force reducing by 11.3% averagely [35].

Framework on chip NOC improvement has advanced an advantageous reaction for versatility issue. Following the occurrence to the NOC improvement, lessening the static force use has been at the purpose of intermingling of innovative work. Since the switches are the most tremendous and rule power eating up modules of NOC, by a wide margin the greater part of the obligations is identified with advance in switch downsized scale building plan. Force gating is at present an astonishing blueprint in this zone at any rate it makes overhead the degree deferrals and in two or three cases it separates the introduction. In this paper, a force competent structure for the system on-chip NoC switches utilizing adaptable directing has been proposed. Our reenactment has demonstrated that we can accomplish close to 80% decreasing in static power use showed up contrastingly comparable to non-power-gated structure and we improved the normal deferral by 35% regarding standard force gated plan [36]. The NoC perspective has been agent as the response for the correspondence repression that Framework on chip SoC presents. Be that as it may, power consumption is one of its significant imperfections. To guarantee that a superior engineering is built, breaking down how force can be diminished in all aspects of the system is fundamental. Force dissemination can be diminished by making changes in accordance with the components in switches. The design itself and the links. This paper will involve

166 □ ISSN: 2722-3221

an overview led on late commitments on NoC. Just as the methods utilized by analysts towards the decrease of power in the switch design, organize engineering and the joins [37]. Pack turned NoC is the mutual in general correspondence foundation for future enormous degree chip multi processors (CMPs). Beginning late, single-cycle multi-bob offbeat repeated traversal (SMART) on repeater-embedded wires to diminish pack delay was proposed. In augmentation, the proposed DOART bolsters virtual channel and is show and coordinating level end free. Exploratory outcomes show that DOART can diminish both the application execution time in addition, sort out power utilization separated and cutting edge NoCs with SMART help [38].

As another time of SoC setup contrive, system on chip NoC, is being gotten by to an ever-expanding degree chips as correspondence designing. In this paper, the NoC arranging issue is assessed, and a low lethargy NoC arranging estimation is proposed to diminish NoC correspondence inertness in arranging unequivocal applications to the NoC structuring. The primer results show that the include proposed in this paper diminishes the execution period of 5 NoC by  $20 \sim 40\%$  and 10%, autonomously, separated and the dynamic arranging and repeated treating figuring [39].

Steadfastness has gotten one of the most earnest issues in arrange on chip NoC. Regardless, how to keep low lethargy and power use while achieving steadfastness is so far a curial challenge. A story scheme for reliable NoCs is proposed. In the arrangement, header ripple is made sure about from change to switch and data is protected through and through. To execute the arrangement, another header security pad in switches is organized, which can check the arranging botches and persevere through the sensitive errors at the same time. As opposed to watching out for each switch, data group is simply decoded and watched out for recipient's framework interface. Thusly, the arrangement ensures trustworthy transmission with lethargy and power usage. Preliminary outcomes show the feasibility of the proposed plan similarly as power usage, latency and area cost [31].

Optical networks-on-chip (ONoCs) has changed into the standard model in the field of multi focus processors, as a key bit of ONoCs, on-chip lasers are the unavoidable wellspring of power use. Especially in work based ONoCs, there are a lot of long Manhattan distance ways which cause bona fide idea hardship. Furthermore, to meet the edge of photograph identifier, the yield intensity of laser must be immeasurably extended [40].

#### 4. CONCLUSION

The NoC are reduce the complex buses designed and also helpless. The one of the main flaws is power consumption. Now we get an excellent progress to reducing the power consumption in the NoC architecture. The major problem is power consumption in the NoC architecture. In this survey we classify the NoC architecture into the main three extent are the name Router architecture, network and links. In these extents include the research work on how to power can handle and saved. After the buffers are mostly used the power consumption in the NoC architecture. Our work on to developed the new methods to overcomes the facility of power consumption in buffers. Similarly, these methods are used for virtual channels and these methods are apply on VCs power consumption. The power consumption methods are used for de-active the resource which is not useful.

The power consumption also issues for the network when they resources are not active for receiving packets. The 3D architecture gives more outcomes to reduce their 2D counters. Moreover, when manage the limits of power in the links then we also to overcomes the limits of power consumption in the NoC architecture. Now if all the methods are including into the only one architecture for most beneficial.

In this paper we define a complete survey on power consumption for reducing methods to on chip style. First of all, we discuss the what is power consumption in the NoC architecture then also discuss in three different areas in the name are router architecture, network architecture and links. Similarly discuss how to improve the efficiency of the power consumption on chip style routers then also discuss the low power methods to be used come out 3D NoC architectures. Particularly apply on the power methods to be overcomes power consumption. Its will be very useful for if the architecture and links can itself optimize in such way that the power saving. The future work on 3D NoC architecture.

### REFERENCES

- [1] M. Baharloo, R. Aligholipour, M. Abdollahi, and A. Khonsari, "Change SUB: A power efficient multiple network-on-chip architecture," *Computers & Electrical Engineering*, vol. 83, pp. 106578, 2020, doi: 10.1016/j.compeleceng.2020.106578.

- [2] D. Xiang, and Q. Pan, "Low-power and high-performance adaptive routing in on-chip networks," *CCF Transactions on High Performance Computing*, vol. 1, no. 2, pp. 92-110, 2019, doi: 10.1007/s42514-019-00009-5.

- [4] P. Wang, S. Niknam, S. Ma, Z. Wang and T. Stefanov, "EVC-based Power Gating Approach to Achieve Low-power and High Performance NoC," in 2019 22nd Euromicro Conference on Digital System Design (DSD), IEEE, 2019, doi: 10.1109/DSD.2019.00027.

- [5] N. L. Venkataraman, R. Kumar and P. M. Shakeel, "Ant lion optimized bufferless routing in the design of low power application specific network on chip," *Circuits, Systems, and Signal Processing*, vol. 39, no. 2, pp. 961-976, 2020, doi: 10.1007/s00034-019-01065-6.

- [6] K. Wang and A. Louri, "CURE: A High-Performance, Low-Power, and Reliable Network-on-Chip Design Using Reinforcement Learning," *IEEE Transactions on Parallel and Distributed Systems*, vol. 31, no. 9, pp. 2125-2138, 2020, doi: 10.1109/TPDS.2020.2986297.

- [7] X. Chen and N. K. Jha, "Reducing wire and energy overheads of the SMART NoC using a setup request network," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 24, no. 10, pp. 3013-3026, Oct 2016, doi: 10.1109/TVLSI.2016.2538284.

- [8] D. Bao, et al, "A Virtual Channel Allocation Algorithm for NoC. in International Conference on Machine Learning and Intelligent Communications," Springer International Publishing, Springer, vol. 227, 2017, doi: 10.1007/978-3-319-73447-7 37.

- [9] A. Bose, and P. Ghosal, "A low latency energy efficient BFT based 3D NoC design with zone based routing strategy," *Journal of Systems Architecture*, vol. 108, pp. 101738, 2020, doi: 10.1016/j.sysarc.2020.101738.

- [10] S. Shenbagavalli and S. Karthikeyan, "An efficient low power NoC router architecture design," in 2015 Online International Conference on Green Engineering and Technologies (IC-GET), IEEE, 2015, doi: 10.1109/GET.2015.7453784.

- [11] C. Effiong, G. Sassatelli, and A. Gamatie, "Distributed and dynamic shared-buffer router for high-performance interconnect," in *Proceedings of the Eleventh IEEE/ACM International Symposium on Networks-on-Chip*, vol. 2, no. 1-8, 2017, doi: 10.1145/3130218.3130223.

- [12] J. Sepúlveda, D. Flórez, M. Soeken, J. Diguet and G. Gogniat, "Dynamic NoC buffer allocation for MPSoC timing side channel attack protection," in 2016 IEEE 7th Latin American Symposium on Circuits & Systems (LASCAS), IEEE, 2016, pp. 91-94, doi: 10.1109/LASCAS.2016.7451017.

- [13] R. Louis, M. Vinodhini and N. S. Murty, "Reliable router architecture with elastic buffer for NoC architecture," in 2015 International Conference on VLSI Systems, Architecture, Technology and Applications (VLSI-SATA), 2015, pp. 1-4, doi: 10.1109/VLSI-SATA.2015.7050463.

- [14] J. M. Joseph, L. Bamberg, I. Hajjar, R. Schmidt, T. Pionteck, & A. Garcia-Ortiz, "Simulation environment for link energy estimation in networks-on-chip with virtual channels," *Integration*, vol. 68, pp. 147-156, 2019, doi: 10.1016/j.vlsi.2019.05.005.

- [15] F. W. B. Zulkefli, P. Ehkan, M. N. M. Warip, & N. Y. Phing, "A efficacy of different buffer size on latency of network on chip (NoC)," *Bulletin of Electrical Engineering and Informatics*, vol. 8, no. 2, pp. 438-442, 2019, doi: 10.11591/eei.v8i2.1422.

- [16] B. Nikolić, S. Tobuschat, L. S. Indrusiak, R. Ernst, & A. Burns, "Real-time analysis of priority-preemptive NoCs with arbitrary buffer sizes and router delays," *Real-Time Systems*, vol. 55, no. 1, pp. 63-105, 2019, doi: 10.1007/s11241-018-9312-0.

- [17] A. Kalimuthu, M. Karthikeyan, "Low Power Network-on-Chip Virtual Channel Router Architecture," *International Journal of Scientific Research and Review*, vol. 7, no. 6, pp. 749-753, 2018.

- [18] P. Wang, S. Niknam, S. Ma, Z. Wang and T. Stefanov, "A novel approach to reduce packet latency increase caused by power gating in network-on-chip," in *Proceedings of the Eleventh IEEE/ACM International Symposium on Networks-on-Chip*, 2017, doi: 10.1145/3130218.3130220.

- [19] H. Farrokhbakht, H. M. Kamali and N. Enright Jerger, "Muffin: Minimally-Buffered Zero-Delay Power-Gating Technique in On-Chip Routers," in 2019 IEEE/ACM International Symposium on Low Power Electronics and Design (ISLPED), IEEE, 2019, pp. 1-6, doi: 10.1109/ISLPED.2019.8824806.

- [20] L. Benini and G. De Micheli, "Networks on chip: A new paradigm for systems on chip design," in *Proceedings 2002 Design, Automation and Test in Europe Conference and Exhibition*, IEEE, 2002, pp. 418-419, doi: 10.1109/DATE.2002.998307.

- [21] N. E. Jerger, T. Krishna, and L.-S. Peh, "On-chip networks" Synthesis Lectures on Computer Architecture, vol. 12, no. 3, pp. 1-210, 2017, doi: 10.2200/S00772ED1V01Y201704CAC040.

- [22] R. Kumar, V. Zyuban and D. M. Tullsen, "Interconnections in multi-core architectures: Understanding mechanisms, overheads and scaling," in 32nd International Symposium on Computer Architecture (ISCA'05), IEEE, 2005, pp. 408-419, doi: 10.1109/ISCA.2005.34.

- [23] G. Dimitrakopoulos, A. Psarras, and I. Seitanidis, "Microarchitecture of Network-on-chip Routers," vol. 1025, Springer, 2015.

- [24] R. Mullins, A. West and S. Moore, "Low-latency virtual-channel routers for on-chip networks," in *Proceedings. 31st Annual International Symposium on Computer Architecture*, IEEE, 2004, pp. 188-197, doi: 10.1109/ISCA.2004.1310774.

- [25] D. R. Melo, C.A. Zeferino, L. Dilillo, E. A. Bezerra, "Maximizing the Inner Resilience of a Network-on-Chip through Router Controllers Design," *Sensors*, vol. 19, no. 24, pp. 5416, 2019, doi: 10.3390/s19245416.

168 🗖 ISSN: 2722-3221

[26] A. N. Udipi, N. Muralimanohar and R. Balasubramonian, "Towards scalable, energy-efficient, bus-based on-chip networks," in HPCA-16 2010 The Sixteenth International Symposium on High-Performance Computer Architecture, IEEE, 2010, pp. 1-12, doi: 10.1109/HPCA.2010.5416639.

- [27] T. Moscibroda and O. Mutlu, "A case for bufferless routing in on-chip networks," in *Proceedings of the 36th annual international symposium on Computer architecture*, pp. 196-207, 2009, doi: 10.1145/1555754.1555781.

- [28] Hang-Sheng Wang, X. Zhu, Li-Shiuan Peh and S. Malik. "Orion: a power-performance simulator for interconnection networks," in 35th Annual IEEE/ACM International Symposium on Microarchitecture, 2002. (MICRO-35), Proceedings, IEEE, 2002, pp. 294-305, doi: 10.1109/MICRO.2002.1176258.

- [29] A. Ben Ahmed, K. Mori and A. Ben Abdallah, "ONoC-SPL: customized network-on-chip (NoC) architecture and prototyping for data-intensive computation applications," in 4th International Conference on Awareness Science and Technology, IEEE, 2012, pp. 257-262, doi: 10.1109/iCAwST.2012.6469623.

- [30] M. U. Tahir, M. R. Naqvi, S. K. Shahzad and M. W. Iqbal, "Resolving Data De-Duplication issues on Cloud," In 2020 International Conference on Engineering and Emerging Technologies (ICEET), pp. 1-5, IEEE, 2020, doi: 10.1109/ICEET48479.2020.9048214.

- [31] M. R. Naqvi, *et al.* "A Concurrence Study on Interoperability Issues in IoT and Decision Making Based Model on Data and Services being used during Inter-Operability," *LGURJCSIT*, vol. 4, no. 4, pp.73-85, 2020.

- [32] M. R. Naqvi, M. A. Jaffar, M. Aslam, S. K. Shahzad, M. W. Iqbal and A. Farooq, "Importance of Big Data in Precision and Personalized Medicine," 2020 International Congress on Human-Computer Interaction, Optimization and Robotic Applications (HORA), IEEE, 2020, pp. 1-6, doi: 10.1109/HORA49412.2020.9152842.

- [33] M. R. Naqvi, M. Aslam, M. W. Iqbal, S. K. Shahzad, M. Malik and M. U. Tahir, "Study of Block Chain and its Impact on Internet of Health Things (IoHT): Challenges and Opportunities," 2020 International Congress on Human-Computer Interaction, Optimization and Robotic Applications (HORA), IEEE, 2020, pp. 1-6, doi: 10.1109/HORA49412.2020.9152846.

- [34] M. R. Naqvi, S. K. Shahzad, M. W. Iqbal, M. Ahmed, M. U. Tahir and B. A. Khan, "Need for Computational and Psycho-linguistics Models in Natural Language Processing for Web Documents," 2020 4th International Symposium on Multidisciplinary Studies and Innovative Technologies (ISMSIT), IEEE, 2020, pp. 1-5, doi: 10.1109/ISMSIT50672.2020.9254754.

- [35] T. Naz, M. Akhtar, S. K. Shahzad, M. Fasli, M. W. Iqbal, and M. R. Naqvi, "Ontology-driven advanced drug-drug interaction," Computers & Electrical Engineering, vol. 86, pp. 106695, 2020, doi: 10.1016/j.compeleceng.2020.106695.

- [36] M. W. Iqbal, N. Ahmad, S. K. Shahzad, M. R. Naqvi, and I. Feroz. "Usability Aspects of Adaptive Mobile Interfaces for Colour-Blind and Vision Deficient Users," International Journal of Computer Science and Network Security, vol. 18, no. 10, pp. 179-189, 2018.

- [37] M. R. Ullah, S. K. Shahzad and M. R. Naqvi, "Challenges and Opportunities for Educational Data Mining in Pakistan," 2019 International Conference on Engineering and Emerging Technologies (ICEET), IEEE, 2019, pp. 1-6, doi: 10.1109/CEET1.2019.8711831.

- [38] N. Tabbasum, et al. "Ontology based Drug-Drug Interaction Model," 1st Conference on Healthcare Computing Systems and Technologies (CHEST 2019), 2020

- [39] U. Rashid, M. W. Iqbal, M. A. Skiandar, M. Q. Raiz, M. R. Naqvi and S. K. Shahzad, "Emotion Detection of Contextual Text using Deep learning," 2020 4th International Symposium on Multidisciplinary Studies and Innovative Technologies (ISMSIT), IEEE, 2020, pp. 1-5, doi: 10.1109/ISMSIT50672.2020.9255279.

- [40] S. Maqbool, M. W. Iqbal, M. R. Naqvi, K. S. Arif, M. A. and M. Arif, "IoT Based Remote Patient Monitoring System," 2020 International Conference on Decision Aid Sciences and Application (DASA), IEEE, 2020, pp. 1255-1260, doi: 10.1109/DASA51403.2020.9317213.

# **BIOGRAPHIES OF AUTHORS**

Muhammad Raza Naqvi is Master Student at Superior University. His Reasearch Intrests are Knowledge technologies, Semantic Web, Knowledge Base Systems.